FPGA高层次综合产业

美国商用软件占主导地位

国内基本空白

在FPGA软件工具设计流程中,虽然前端流程可借助第三方工具,其余环节却需FPGA芯片厂商自主研发,形成较高技术壁垒。国内外FPGA厂商均推出自研综合工具:Xilinx推出Vitis统一软件平台,助力软件开发;Altera提供Quartus

II设计工具;Lattice则有Diamond。国内方面,紫光同创的Pango Design

Suite支持千万门级FPGA设计,安路科技的TangDynasty、复旦微的procise综合工具,也呈现出不俗水平。

FPGA软硬件相互影响,尤其在高端大规模FPGA领域,设计流程往往以软件先导。事实上,软件工具研发水平直接决定硬件性能和规模的达成。随着国产FPGA制程进展,下一代超1KK的大容量产品已是趋势,在这个新的发展阶段,高层次综合显得愈发重要。眼下,填补国内在这一领域的大面积空白,势在必行。

EDA工具链最前端

HLS高层次综合

助力芯片敏捷开发

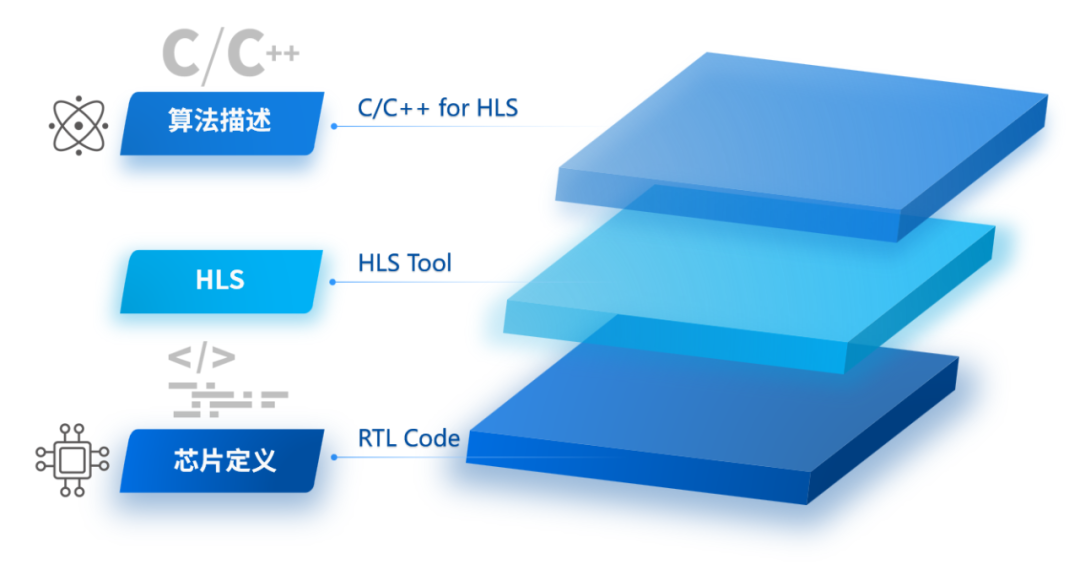

高层次综合(High-level

Synthesis)简称HLS,是一项引领着现代设计革命的前沿技术,致力于将高层次语言描述的智能逻辑结构,迅速转变为低抽象级语言描述的精密电路模型。高层次语言,包括广受欢迎的C、C++、SystemC等,以其高度抽象的特性,赋予设计者灵活的表达能力,无需涉足繁琐的时钟和时序细节。相对应地,低层次语言如Verilog、VHDL、SystemVerilog,则专注于时钟周期精确(cycle-accurate)

的寄存器传输级电路模型描述,在当前的ASIC或FPGA设计中被广泛运用,构成了主要的电路建模和描述方法。然而,在当今激烈的商业竞争中,速度与效率愈加重要。

MLSynthesis是一款突破性的创新产品,旨在将高层次语言描述的逻辑结构,智能转换为低抽象级语言描述的电路模型。无需耗费繁琐的时间和资源,MLSynthesis将您的创意迅速转化为实质,实现芯片敏捷设计。与传统的人工优化RTL相比,MLSynthesis在效率和结果上多方面胜出,为数字设计领域带来了前所未有的便利和效益。

我们很高兴地宣布 MLSynthesis 发布全新版本V0.5,

该版本引入了许多令人振奋的新特性,

旨在进一步提升用户体验和工作效率。

特性1:

支持Chisel testbench自动生成

MLSynthesis最新版本引入了Chisel

Testbench的自动生成功能。可使用户能够快速创建Chisel测试,而无需手动编写繁琐的测试代码。同时,MLSynthesis还提供了18个常见的测试用例,覆盖了广泛的应用场景,从而为用户提供了全方位的验证工具。这一自动化的测试套件不仅极大地简化了验证流程,同时确保了更便捷的测试覆盖,有助于提高设计的稳健性和可靠性。

特性2:

支持任意循环展开

(完全展开+部分展开)

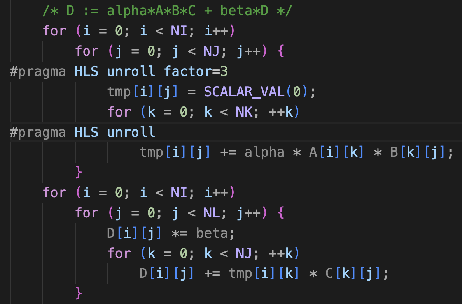

在HLS中,UNROLL pragma是一种指令,用于控制循环的展开(unrolling)。循环展开是一种优化技术,通过增加每次迭代的计算量,从而减少循环的迭代次数,以提高硬件的性能。

当涉及到在RTL设计中创建循环体的多个副本以实现并行性时,UNROLL pragma为用户提供了一种有力的手段。这个 pragma 允许用户扩展循环,从而创建多个独立的操作,而不是单一的操作集合。

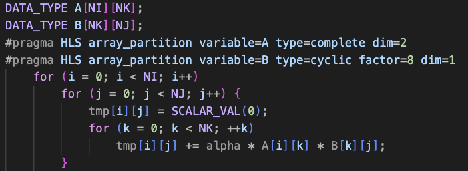

用户只需要在c++循环内增加#pragma HLS

unroll即可使用,使用示例如下,将对j的循环进行全部循环展开,然后将对i的循环进行部分循环展开,且循环展开因子factor为3。

▲ 图1

UNROLL

pragma示例

通过使用UNROLL

pragma,用户可以选择展开整个循环或者部分展开循环。完全展开循环将在RTL中为每个循环迭代创建循环体的副本,使整个循环能够同时运行。而部分展开循环允许用户指定一个循环展开因子factor,创建循环体的factor个副本,从而相应地减少循环迭代,若循环次数不能被factor整除,剩余循环体会附在展开的循环体后。这种方式可以有效地提高数据访问和吞吐量,提高执行效率。然而,展开因子的选择需要根据硬件资源、循环体内的计算复杂性以及特定应用的需求来调整。在某些情况下,循环展开可能会导致资源占用过多,因此需要谨慎使用。

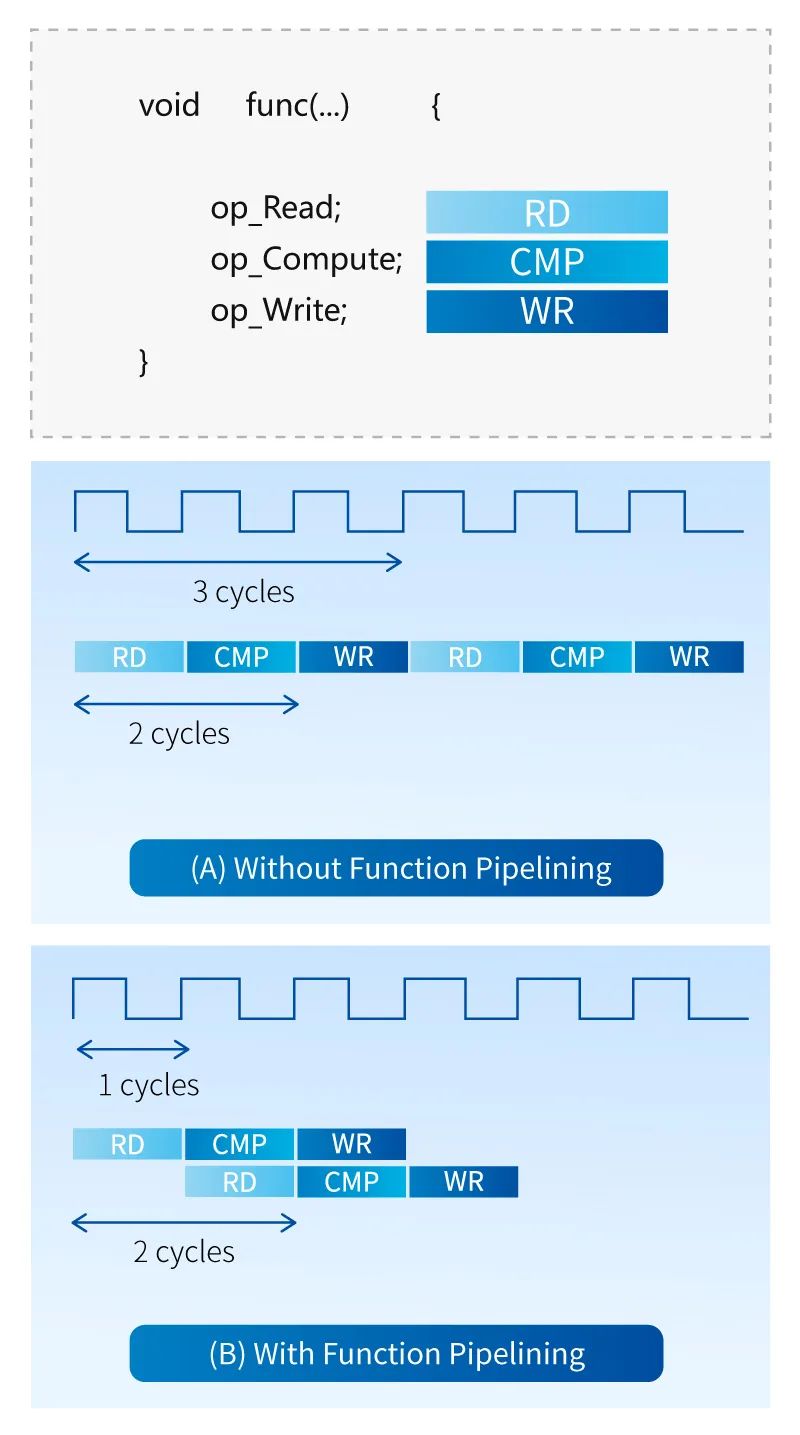

Pipelining的意思是一个操作并不需要完成所有的步骤,而下一个操作就会开始,可以用于函数和循环。

▲ 图2 Task Pipelining

在HLS中,Pipeline Pragma是一种用于指导硬件生成流水线的指令。流水线是一种优化技术,通过将计算任务分为一系列阶段,使得多个阶段的计算可以并行执行,从而提高硬件的吞吐量。

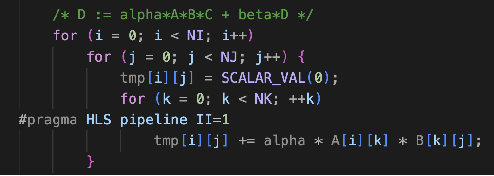

MLSynthesis支持通过流水打拍来缩短函数或循环的启动时间间隔(II),期望II可为任意正整数,但实际结果可能更大。

为了实现这一点,您只需在最内层循环或函数中添加 pragma。以下是一个示例,将对变量 k 的循环的期望 II 设置为1。请注意,根据数据依赖关系和资源情况,实际结果的 II 可能大于1。以示例

demo/resource.json 中的资源和 kernel_2mm 的依赖关系为例,合法的下界为10,因此实际处理将按照10来执行。

▲ 图3 Pipeline Pragma示例

使用Pipeline

Pragma的好处在于,它允许对循环进行流水线优化,提高硬件的性能和吞吐量。然而,流水线的效果可能受到硬件资源、数据依赖性以及特定应用的影响。因此,调整和优化流水线需要根据具体情况进行。

HLS中的Array Partition Pragma是一种指令,用于控制在FPGA硬件上生成的硬件描述中的数组分区方式。通过使用Array Partition

Pragma,您可以指定如何将数组拆分为更小的存储单元,以便更好地适应硬件资源。

以下是一个简要的介绍Array Partition Pragma的示例, #pragma HLS ARRAY_PARTITION 指令被用于数组

A,指定按照8的展开因子进行block分区,这将帮助优化硬件生成,数组 A 将被拆分为多个小数组,以更好地利用FPGA硬件资源。

▲ 图4 Array Partition

Pragma示例

使用Array Partition Pragma的好处在于,您可以根据应用的需求和硬件架构的特点来优化数组的存储和访问方式,从而提高FPGA设计的性能和效率。

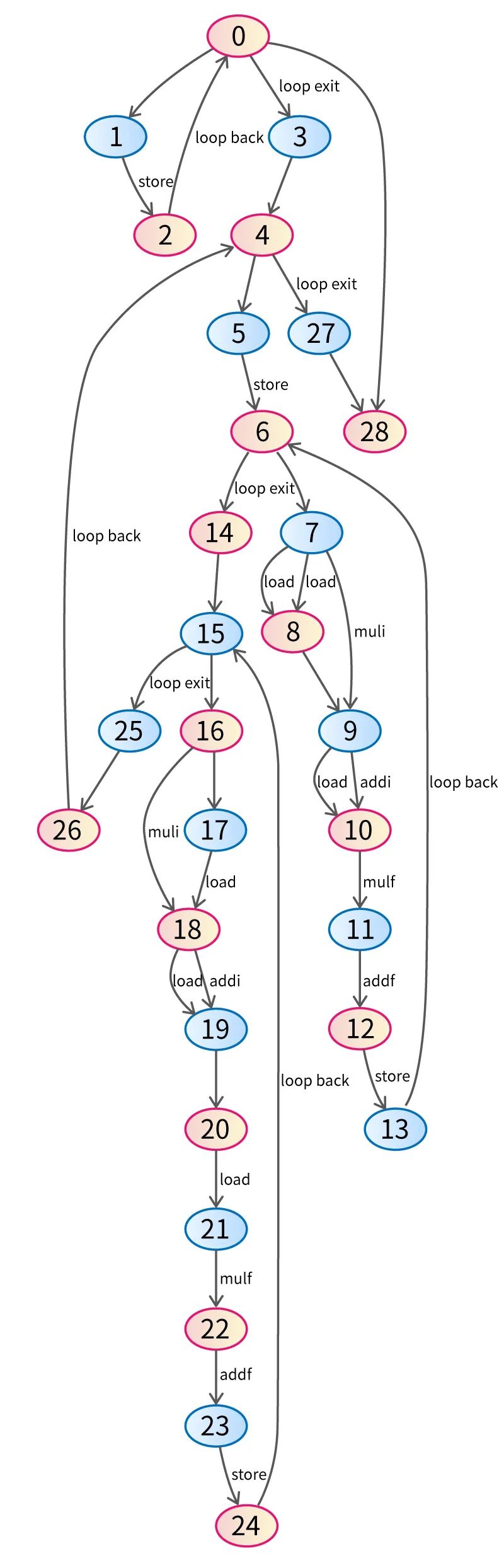

MLSynthesis新版本引入了可视化调度图新特性。用户现在可以通过直观的调度图一览所有操作的数据流和顺序,使复杂的任务调度过程一目了然。这一增强功能不仅提高了用户对整个工作流的可视化理解,也使得调试和优化变得更加直观和高效。

MLSynthesis支持同时使用sbt和mill进行编译。这一灵活性的增加意味着用户可以选择他们更喜欢的构建工具,从而更好地满足其工作流和项目需求。

MLSynthesis数据重复读写访问操作,通过数据流依赖性分析,引入中间结果复用、冗余读写删除优化,显著降低了对存储器的冗余访问次数。这不仅有效减轻了存储器系统的负担,提高了内存带宽利用率,同时也显著提升了硬件性能和资源利用效率。这项优化对于嵌入式系统和FPGA等硬件设计中的高性能要求至关重要。

MLSynthesis新增mem2reg优化,mem2reg是编译器中一项强大的优化功能,旨在通过将内存操作转换为寄存器操作来提高程序性能。它在处理SSA形式的中间表示时发挥作用,通过识别临时变量的生命周期并将其提升到寄存器,减少了内存访问的开销。这不仅简化了生成的代码结构,还有助于优化处理复杂数据结构(如数组或结构体)的代码,提升电路设计整体执行效率。

MLSynthesis最新版本引入了对Vivado

IP的自动生成和调用的新特性。这一特性涵盖了常见的浮点数IP库,使用户能够更灵活地配置资源。通过简单地编辑资源配置文件(resource.json),用户可以指定所需的IP以及相应的延迟和配置参数。

这一新特性的核心优势在于自动选择和集成IP,根据用户的配置自动生成适当的Vivado

IP模块。这不仅降低了集成过程的复杂性,同时也加速了设计迭代的速度。这一改进大大提高了MLSynthesis的灵活性和用户友好性。

MLSynthesis最新版本引入了多函数存储接口优化,通过将多个模块间的存储器调用控制巧妙封装在程序内部,使用户能够更轻松、更便捷地进行存储器操作。这一创新简化了存储器接口的管理,为用户提供了更高的灵活性和易用性,进一步优化了整体设计流程。

MLSynthesis引入了全新的Debugger功能,支持从scf、tor、hec等多个Dialect进行仿真模拟。这一功能大大增强了逐层验证仿真的灵活性,用户现在能够更轻松地开发和设计新的优化,同时以更全面的视角审视各个阶段的模拟结果,提升整体开发效率。

MLSynthesis新增了超过20+

MLIR算子的全面支持。这意味着用户现在可以利用更丰富的算子集合,更灵活地构建和优化他们的设计。这一扩展使MLSynthesis在电路设计和优化方面具备了更大的表达能力和适用性,为用户提供了更广泛的选择和更精细的控制。

支持的算子包括:

整数运算:

AddIOp、SubIOp、 MulIOp、 DivSIOp、 RemSIOp、

DivUIOp、 RemUIOp、AndIOp、 OrIOp、 XOrIOp、 CmpIOp、 ShLIOp、 ShRSIOp、 ShRUIOp

浮点数运算:

AddFOp、 SubFOp、 MulFOp、 DivFOp、 CmpFOp、

NegFOp

转换运算:

IndexCastOp、 SIToFPOp、 FPToSIOp、 ExtFOp、

ExtSIOp、 ExtUIOp、 TruncIOp、 TruncFOp

数学函数:

AbsFOp、 AbsIOp、 CeilOp、 FloorOp、 RoundOp、

ExpOp、 PowFOp、 SqrtOp、 LogOp、 ErfOp、 CosOp、 TanOp、 TanhOp、 SinOp

我们相信这些新特性将为MLSynthesis的用户带来更多可能性和便利。如果您对试用MLSynthesis或进一步了解详情感兴趣,请随时与我们联系,我们将竭诚为您服务。

MLSynthesis@pkueda.org.cn