EDA工具链最前端 |

HLS高层次综合助力芯片敏捷开发

高层次综合(High-level

Synthesis)简称HLS,是一项引领着现代设计革命的前沿技术,致力于将高层次语言描述的智能逻辑结构,迅速转变为低抽象级语言描述的精密电路模型。高层次语言,包括广受欢迎的C、C++、SystemC等,以其高度抽象的特性,赋予设计者灵活的表达能力,无需涉足繁琐的时钟和时序细节。相对应地,低层次语言如Verilog、VHDL、SystemVerilog,则专注于时钟周期精确(cycle-accurate)

的寄存器传输级电路模型描述,在当前的ASIC或FPGA设计中被广泛运用,构成了主要的电路建模和描述方法。然而,在当今激烈的商业竞争中,速度与效率愈加重要。

MLSynthesis(Multi-Level

Synthesis)不仅仅是一款产品,更是您在AI&数字化时代的强大伙伴。借助MLSynthesis,高层次语言如C、C++等的高度抽象特性能够被智能解析和转化,使得算法、软件、硬件设计师能够更专注于创意的发挥,而无需为繁琐的底层细节担忧。

无论您是正在追求创新的科技公司,还是计划在芯片设计领域掀起一场变革的企业,MLSynthesis都将是您的最佳合作伙伴。MLSynthesis不仅缩短了产品开发周期,也提升了设计效率,使得您的团队能够更快地将创意变为现实,并以更高的竞争力在市场中脱颖而出。

MLSynthesis是一款突破性的创新产品,旨在将高层次语言描述的逻辑结构,智能转换为低抽象级语言描述的电路模型。无需耗费繁琐的时间和资源,HECTOR将您的创意迅速转化为实质,实现芯片敏捷设计。与传统的人工优化RTL相比,HECTOR在效率和结果上多方面胜出,为数字设计领域带来了前所未有的便利和效益。

HLS市场分析:FPGA高层次综合产业美国商用软件占主导地位

高层次综合(High-level

Synthesis)简称HLS,是一项引领着现代设计革命的前沿技术,致力于将高层次语言描述的智能逻辑结构,迅速转变为低抽象级语言描述的精密电路模型。高层次语言,包括广受欢迎的C、C++、SystemC等,以其高度抽象的特性,赋予设计者灵活的表达能力,无需涉足繁琐的时钟和时序细节。相对应地,低层次语言如Verilog、VHDL、SystemVerilog,则专注于时钟周期精确(cycle-accurate)

的寄存器传输级电路模型描述,在当前的ASIC或FPGA设计中被广泛运用,构成了主要的电路建模和描述方法。然而,在当今激烈的商业竞争中,速度与效率愈加重要。

MLSynthesis(Multi-Level

Synthesis)不仅仅是一款产品,更是您在AI&数字化时代的强大伙伴。借助MLSynthesis,高层次语言如C、C++等的高度抽象特性能够被智能解析和转化,使得算法、软件、硬件设计师能够更专注于创意的发挥,而无需为繁琐的底层细节担忧。

无论您是正在追求创新的科技公司,还是计划在芯片设计领域掀起一场变革的企业,MLSynthesis都将是您的最佳合作伙伴。MLSynthesis不仅缩短了产品开发周期,也提升了设计效率,使得您的团队能够更快地将创意变为现实,并以更高的竞争力在市场中脱颖而出。

MLSynthesis

高灵活性算法-芯片协同设计驱动FPGA应用快速落地

MLSynthesis

竞争优势简介

MLSynthesis 竞争优势 基于MLIR的更快速高层次综合

MLSynthesis 竞争优势 支持适配不同FPGA,允许用户自定义IP实现

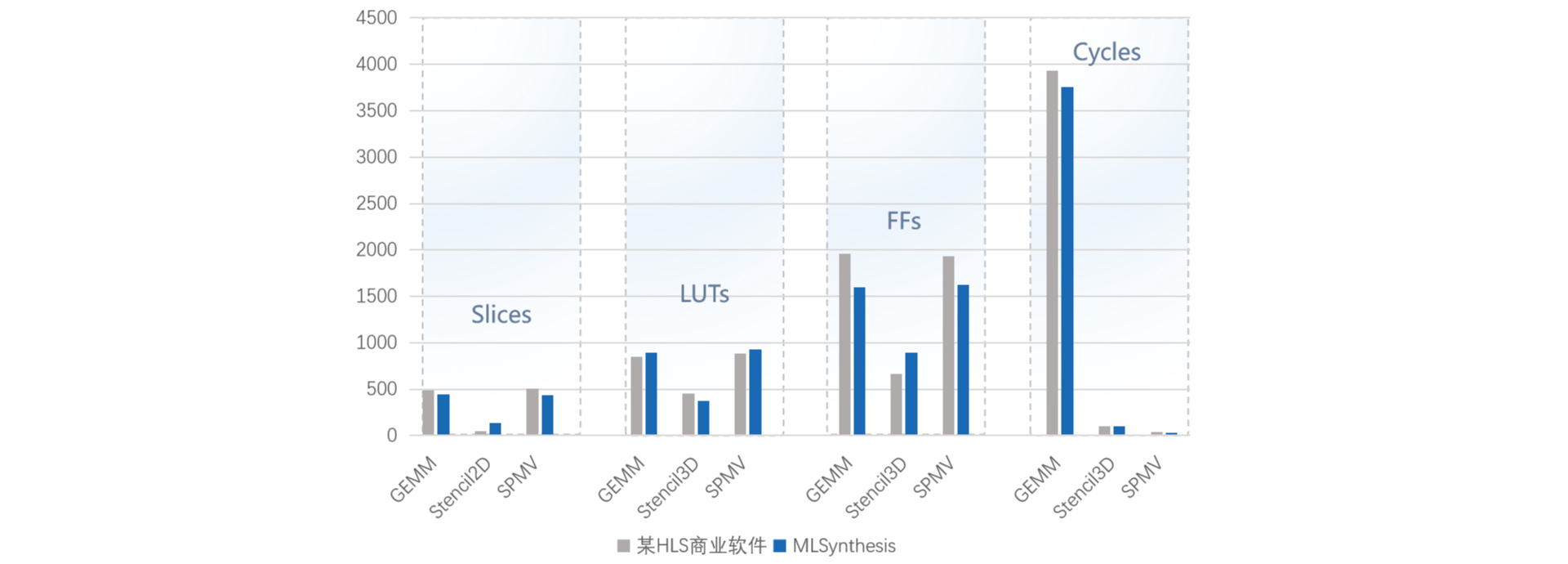

MLSynthesis 竞争优势 更佳性能,Cycle、LUT、FF

最后,非常欢迎您与我们联系,以 进一步 了解并试用

MLSynthesis 。我们为您准备了60+个测试用例,让您可以全面地体验 MLSynthesis 带来的便捷和优势。这些测试用例将帮助您深入了解 MLSynthesis

在不同情况下的表现,并感受其高效的特性。

我们期待着为您提供这一全面的体验,以及帮助您深入了解

MLSynthesis 所带来的创新性和效益。如果您对试用 MLSynthesis 或进一步了解详情感兴趣,请随时与我们联系,我们将竭诚为您服务。

联系我们:digital_eda@pkueda.org.cn